- 您现在的位置:买卖IC网 > Sheet目录1201 > CIC-FILT-X2-UT2 (Lattice Semiconductor Corporation)SITE LICENSE CIC LATTICEXP2 CONF

�� �

�

Lattice� Semiconductor�

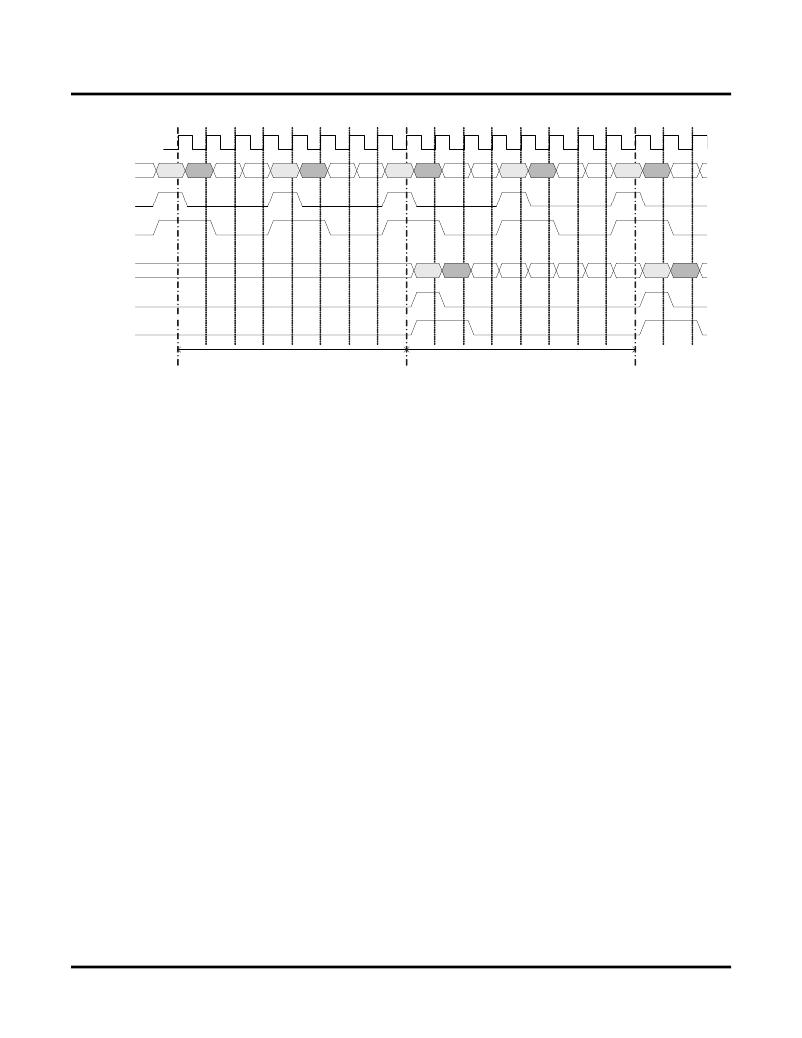

�(d)� Dual-Channel:� Inputs� are� sampled� in� every� two� clock� cycles:�

�clk�

�Functional� Description�

�din�

�x(0)�

�u� (0)�

�x(1)�

�u� (1)�

�x(2)�

�u� (2)�

�x(3)�

�u� (3)�

�x(4)�

�u� (4)�

�i� b� start�

�inp� v� alid�

�do� u� t�

�y� x� (0)�

�y� u� (0)�

�y� x� (1)�

�y� u� (1)�

�o� b� start�

�o� u� t� v� alid�

�Filter� Latency� +� 4*� Rate� Clock� Cycles�

�4*� Rate� Clock� Cycles�

�Interpolator� Timing�

�The� interface� timing� for� four� cases� of� interpolators� are� presented� in� Figure� 2-4� and� a� brief� description� of� each� case�

�is� given� below.� The� up-sampling� rate� is� equal� to� 2� (� Rate� =� 2)� for� all� cases� described.�

�?� Figure� 2-3� (a):� A� new� input� sample� is� available� in� every� Rate� clock� cycles,� so� inpvalid� signal� during� those�

�cycles.� The� CIC� will� activate� the� rfi� signal� when� it� is� ready� to� read� the� next� sample.� When� rfi� is� inactive,� the�

�CIC� cannot� accept� a� new� input� sample� in� the� next� clock� cycle.� The� output� samples� are� available� continuously,�

�after� the� initial� latency.�

�?� Figure� 2-3� (b):� A� new� input� sample� is� available� in� every� 2*� Rate� clock� cycles.� The� IP� core� will� deactivate� the� rfi�

�signal� for� (� Rate� -� 1)� clock� cycles� when� a� sample� is� inputted.� When� rfi� is� inactive,� IP� core� cannot� accept� a� new�

�input� sample� in� the� next� clock� cycle.� After� a� few� clock� cycles� of� the� first� input� sample� to� the� IP� core,� the� ?�

�outvalid� signal� will� be� asserted� for� Rate� clock� cycles� to� indicate� the� output� samples� interpolated� from� the� first�

�input� sample� are� available.� Then,� subsequent� output� samples� will� be� available� for� Rate� clock� cycles� in� every�

�2*� Rate� clock� cycles� intermittently.�

�?� Figure� 2-3� (c):� Interlaced� dual-channel� input� samples� x� and� u� are� supplied� in� every� 2*� Rate� clock� cycles,� so�

�ibstart� signal� is� high� in� every� Rate� clock� cycles� during� the� first� channel� sample� x� input.� The� IP� core� will� deac-�

�tivate� rfi� signal� for� 2*(� Rate� -� 1)� clock� cycles� happened� before� the� last� channel� input.� When� rfi� is� inactive,� IP�

�core� cannot� accept� a� new� block� of� input� samples� in� the� next� clock� cycle.� After� a� few� clock� cycles� of� the� first� input�

�sample� to� the� IP� core,� the� outvalid� signal� will� be� asserted� to� indicate� the� output� sample� yx� for� x� and� yu� for� u�

�are� available.� The� signal� obstart� indicates� data� for� the� first� channel.� Then,� subsequent� output� samples� will� be�

�available� continuously.�

�?� Figure� 2-3� (d):� Interlaced� dual-channel� input� samples� x� and� u� are� supplied� in� every� 4*� Rate� clock� cycles.� The� IP�

�core� will� deactivate� the� rfi� signal� for� 2*(� Rate� -� 1)� clock� cycles� before� the� last� channel� input.� When� rfi� is� inac-�

�tive,� the� IP� core� cannot� accept� a� new� input� sample� in� the� next� clock� cycles.� After� a� few� clock� cycles� of� the� first�

�input� sample� to� the� IP� core,� the� outvalid� signal� will� be� asserted� to� indicate� the� output� sample� yx� for� x� and� yu�

�for� u� are� available.� The� signal� obstart� indicates� data� for� the� first� channel.� Then,� subsequent� output� samples�

�will� be� available� for� 2*� Rate� clock� cycles� in� every� 4*� Rate� clock� cycles� intermittently.�

�IPUG42_02.6,� August� 2010�

�15�

�Cascaded� Integrator-Comb� (CIC)� Filter� User’s� Guide�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CJ70-29

TRB CABLE JACK CRIMP STR CABLE

CJ70-47

TRB CABLE JACK WRENCH CRIMP STR

CL-80

CURRENT LIMITER INRUSH

CL-DEMOKIT-CAN40

CHROMALIT DEMO KIT

CM2009-00QR

VGA PORT COMPANION-65 OHM QSOP16

CMF-RD50-10-0

CPTC FUSE RESETTABLE

CMF-RLC50-10-0

CPTC FUSE RESETTABLE

CMF-RQ50-10-0

CPTC FUSE RESETTABLE

相关代理商/技术参数

CIC-FILT-XM-U2

功能描述:开发软件 Cascaded Integrator Comb Filter RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

CIC-FILT-XM-UT2

制造商:Lattice Semiconductor Corporation 功能描述:

CICG100B560

制造商:Thomas & Betts 功能描述:Connector Accessories Cord Connector Steel

CICG100B750

制造商:Thomas & Betts 功能描述:Connector Accessories Cord Connector Steel

CICG100B850

制造商:Thomas & Betts 功能描述:Connector Accessories Cord Connector Steel

CICG100C1050

制造商:Thomas & Betts 功能描述:Connector Accessories Cord Connector Steel

CICG100C950

制造商:Thomas & Betts 功能描述:Connector Accessories Cord Connector Steel

CICG125C950

制造商:Thomas & Betts 功能描述:Connector Accessories Cord Connector Steel